-

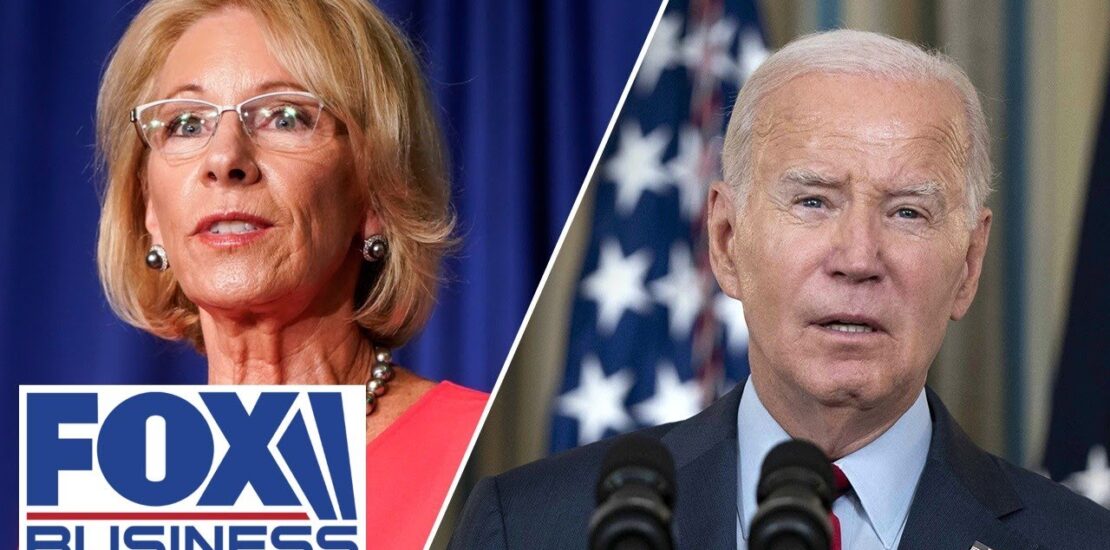

WATCH: “AI Legalese Decoder Dissects Former Education Secretary’s Critique of Biden’s Vote-Buying Scheme”

- April 18, 2024

- Posted by: legaleseblogger

- Category: Related News

No Comments

-

Unlocking Legal Jargon: How AI Legalese Decoder Can Benefit Small Business Owners in the 2024 ICCC Program

- April 17, 2024

- Posted by: legaleseblogger

- Category: Related News

-

Unlocking Education Opportunities: How AI Legalese Decoder Can Future-Proof Your Child’s Education

- April 13, 2024

- Posted by: legaleseblogger

- Category: Related News

-

Understanding the Legal and Behavioral Implications of a Partner’s Gambling Problem with AI Legalese Decoder

- April 13, 2024

- Posted by: legaleseblogger

- Category: Related News

-

Unlocking the GI Bill: How AI Legalese Decoder Can Help Couples Navigate the Path to Education Benefits for Children Born Late in a Military Career

- April 12, 2024

- Posted by: legaleseblogger

- Category: Related News

-

Empowering Future Lawyers: How AI Legalese Decoder Can Revolutionize Legal Education and Practice

- April 8, 2024

- Posted by: legaleseblogger

- Category: Related News

-

AI Legalese Decoder: Revolutionizing Legal Education for Two New Business Degrees at WT

- March 29, 2024

- Posted by: legaleseblogger

- Category: Related News

-

WATCH: “Demystifying the USA Study Visa Big Update 2024: How AI Legalese Decoder Can Help + UK Tightens Regulations. Join Our Live Session Tuesday 8pm”

- March 29, 2024

- Posted by: legaleseblogger

- Category: Related News

-

WATCH: “The AI Legalese Decoder: Simplifying Legal Jargon for Minnesota’s Pea Protein Alt-Meat Revolution”

- March 26, 2024

- Posted by: legaleseblogger

- Category: Related News

-

Unlocking Google Chromebook’s Education Potential: How AI Legalese Decoder Can Simplify Complex Features for Educators

- March 23, 2024

- Posted by: legaleseblogger

- Category: Related News

****** just grabbed a 7 Day Free Trial Pro Plan with Contract Analyzer

****** just grabbed a 7 Day Free Trial Pro Plan with Contract Analyzer